Error 404 - Not Found

Sorry, but you are looking for something that isn't here.

Support This Site:

Bitcoin, by popular demand: 1NrrHYZMum2JaHJeSZufFiTqg9W8uNdfzM (Please verify PGP Signature !)-

-

-

Recent Comments:

- Soluted on "Where Lisp Fails: at Turning People into Fungible Cogs."

- Aiken Drum on "MicroWriter Redux."

- Stanislav on "MicroWriter Redux."

- Aiken Drum on "MicroWriter Redux."

- SquintyEyes on "A Complete Pill for the Sage SmartProbe."

- Stanislav on "A Complete Pill for the Sage SmartProbe."

- SquintyEyes on "A Complete Pill for the Sage SmartProbe."

- James Pelham on "Going Nowhere Really Fast, or How Computers Only Come in Two Speeds."

- Stanislav on "Seven Laws of Sane Personal Computing"

- tuhdo on "Seven Laws of Sane Personal Computing"

- Anonymous on "The Three Reasons For Source Code Publication."

- hapax on "FFA for DOS!"

- John Doe on "Intro, Part II."

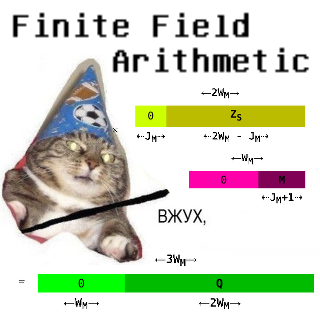

- Stanislav on "“Finite Field Arithmetic.” Chapter 18B: "Cutouts" in Peh."

- hapax on "“Finite Field Arithmetic.” Chapter 18B: "Cutouts" in Peh."

- Samuel on "Why Hypercard Had to Die"

- Stanislav on "MicroWriter Redux."

- robert on "MicroWriter Redux."

- Verisimilitude on ""Pest" v. 0xFB."

- Hayley Patton on "The Three Reasons For Source Code Publication."

- Stanislav on "How to Make Your Own Lamport Parachute from Common Household Materials."

- GTP on "How to Make Your Own Lamport Parachute from Common Household Materials."

- Stanislav on "A "Cement"-Maker for TRB."

- Verisimilitude on "A "Cement"-Maker for TRB."

- Verisimilitude on "The V Public License."

Categories

- Ada (38)

- Bitcoin (87)

- Books (10)

- Chorder (2)

- Chumpatronics (18)

- Cold Air (110)

- Computation (98)

- Copyrasty (11)

- Cryptography (72)

- Distractions (60)

- FFA (36)

- FG (8)

- FPGA (13)

- Friends (79)

- FritzChip (1)

- Gentoo (7)

- Hardware (63)

- Hot Air (67)

- Idea (20)

- Lisp (35)

- LispMachine (14)

- LoperOS (20)

- MacIvory (4)

- Mathematics (75)

- Memory (7)

- MIPS (3)

- MIT (2)

- ModestProposal (29)

- NonLoper (132)

- P2P (5)

- Papers (5)

- Pest (5)

- Philology (7)

- Philosophy (56)

- Photo (33)

- Physics (10)

- Predictions (6)

- Progress (13)

- Reactions (3)

- Reversing (23)

- SerpentCipher (11)

- Services (9)

- ShouldersGiants (60)

- SoftwareArchaeology (77)

- SoftwareSucks (125)

- Symbolics (12)

- TeX (1)

- Translations (5)

- TRB (2)

- Urbit (6)

- VPL (1)

- VTronics (9)

- X-Ray (7)

About

Collaborations

Fundamental Classics

- A Measure of Sacrifice

- Artificial Intelligence Meets Natural Stupidity

- Ethics for Programmers: Primum non Nocere

- Industry's Parting Gifts

- Post-Soviet Lessons for a Post-American Century

- Reflections on Trusting Trust

- Software Does Not Fail

- The Decline and Fall of the British University

- The Imagination Gap

- The Myth of the Rule of Law

- The Playdough Protocols

- The Right to Read

- What Colour are Your Bits?

- You and the Atomic Bomb

People

- Abstract Heresies

- Alexandru-Dan Corlan

- Alexey Guzey

- Angry Unix Programmer

- Arcane Sentiment

- ave1

- Axis of Eval

- Cgra

- David Gregory

- Don Lancaster

- Doron Zeilberger

- Erik Naggum

- Fabien Sanglard

- Greg Egan

- IgnorantGuru

- Ilkka Kokkarinen

- Irreal

- James Hague

- John Savard

- John Walker

- Lambda the Ultimate

- Lemonodor

- Lichtblau

- Mark Tarver

- Micro_Research

- mod6

- Pascal Costanza

- Peter Woit

- Planet Lisp

- Scott Locklin

- shinohai

- Simon Plouffe

- Structural Insight

- Ted Nelson

- Terry Davis

- The Tar Pit

- Thimbron

- Trinque

- Uncle Al

- Unenumerated

- Verisimilitudes

- Xah Lee

Popular Articles

- "The Advantages of a Dragon."

- A Country of Which Nothing is Known but the Name.

- Bitcoin, or How to Hammer in Nails with a Microscope.

- Buy Rotting Bits, Or Else: The War on Libraries.

- Don’t Blame the Mice

- Engelbart’s Violin

- For Your Eyes Only

- Going Nowhere Really Fast, or How Computers Only Come in Two Speeds.

- Modern Chumpatronic Engineering.

- No Formats, no Format Wars.

- Non-Apple’s Mistake

- Of Lisp Macros and Washing Machines

- Practical Blockchain Telegraphy.

- Sage SmartProbe FAQ

- Seven Laws of Sane Personal Computing

- Shards of Lost Technology, and the Need for High-Level Architectures.

- Steam Lisp

- Stierlitz, the Fearless, Driver-Less Bus Analyzer.

- The Google H1 Fritz Chip.

- The Wisdom of Erik Naggum

- Thumbs Down for Clojure

- To Lend is the Right of an Owner – That is, Not You.

- Where Lisp Fails: at Turning People into Fungible Cogs.

- Why Hypercard Had to Die

- You have made your bedrock, now lie in it.

Projects

Toys

Useful and Interesting

- Ada Reference Manual

- ada-ru.org

- archive.is

- Ben Vulpes's VTronics Intro

- Bitdash Crawler

- bitsavers.org

- Common Lisp Hyperspec

- Erik Naggum Archive

- GNAT Reference Manual

- Marginalia

- Pestnet Logs

- PGPgram/Pubkey Dissector

- Phf's #t Logs

- Phf's V-Tree Browser

- PRC68

- sandpile.org

- Systemd-Free Linux

- TBOBLAP

- YArchive

- Zeptobars

- Флибуста

Vintage

Archives

- February 2024

- September 2022

- February 2022

- January 2022

- December 2021

- November 2021

- September 2021

- March 2021

- January 2021

- December 2020

- June 2020

- May 2020

- April 2020

- February 2020

- January 2020

- November 2019

- October 2019

- August 2019

- July 2019

- June 2019

- May 2019

- April 2019

- March 2019

- February 2019

- January 2019

- December 2018

- November 2018

- October 2018

- September 2018

- July 2018

- June 2018

- May 2018

- April 2018

- February 2018

- January 2018

- December 2017

- November 2017

- May 2017

- January 2017

- October 2016

- September 2016

- July 2016

- June 2016

- April 2016

- March 2016

- December 2015

- October 2015

- August 2015

- May 2015

- June 2014

- April 2014

- March 2014

- January 2014

- December 2013

- November 2013

- October 2013

- September 2013

- July 2013

- May 2013

- April 2013

- February 2013

- January 2013

- October 2012

- September 2012

- August 2012

- June 2012

- May 2012

- April 2012

- March 2012

- February 2012

- January 2012

- December 2011

- November 2011

- October 2011

- July 2011

- May 2011

- April 2011

- March 2011

- January 2011

- November 2010

- September 2010

- August 2010

- July 2010

- June 2010

- April 2010

- March 2010

- February 2010

- January 2010

- December 2009

- October 2009

- September 2009

- August 2009

- July 2009

- June 2009

- May 2009

- March 2009

- February 2009

- January 2009

- December 2008

- September 2008

- August 2008

- July 2008

- June 2008

- May 2008

- February 2008

- January 2008

- December 2007

- November 2007

Meta

Copyright © 2025 Stanislav Datskovskiy · Any views or opinions presented on this site are solely those of the author, Stanislav Datskovskiy, and do not necessarily represent those of his clients, employers, or associates. All information on this site is provided as-is, with no warranties whatsoever.